# MEMORY COMPONENTS

# 65,536 x 1-BIT DYNAMIC RAM MK4564(P/N/J/E)-15/20

### FEATURES

- Recognized industry standard 16-pin configuration from Mostek

- □ Single +5V (± 10%) supply operation

- On chip substrate bias generator for optimum performance

- Low power: 300 mW active, max 22 mW standby, max

- 150 ns access time, 260 ns cycle time (MK4564-15) 200 ns access time, 330 ns cycle time (MK4564-20)

#### DESCRIPTION

The MK4564 is the new generation dynamic RAM. Organized 65,536 words by 1 bit, it is the successor to the industry standard MK4116. The MK4564 utilizes Mostek's Scaled POLY 5 process technology as well as advanced circuit techniques to provide wide operating margins, both internally and to the system user. The use of dynamic circuitry throughout, including the 512 sense amplifiers, assures that power dissipation is minimized without any sacrifice in speed or internal and external operating margins. Refresh characteristics have been chosen to maximize yield (low cost to user) while maintaining compatibility between dynamic RAM generations.

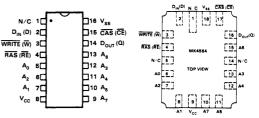

RAS (RE)

WRITE (W)

V<sub>cc</sub>

V<sub>SS</sub> N/C Row Address

Write Input

Power (5V)

Not Connected

Strobe

Read/

GND

#### PIN FUNCTIONS

An-Az

D<sub>IN</sub> (D)

D<sub>OUT</sub> (Q)

CAS (CE)

- □ Extended D<sub>OUT</sub> hold using CAS control (Hidden Refresh)

- Common I/O capability using "early write"

- Read, Write, Read-Write, Read-Modify-Write and Page-Mode capability

- □ All inputs TTL compatible, low capacitance, and protected against static charge

- □ Scaled POLY 5<sup>TM</sup> technology

- 128 refresh cycles (2 msec) Pin 9 is not needed for refresh

Multiplexed address inputs (a feature dating back to the industry standard MK4096, 1973) permit the MK4564 to be packaged in a standard 16-pin DIP with only 15 pins required for basic functionality. The MK4564 is designed to be compatible with the JEDEC standards for the 64K x 1 dynamic RAM.

The output of the MK4564 can be held valid up to 10  $\mu$ sec by holding CAS active low. This is quite useful since refresh cycles can be performed while holding data valid from a previous cycle. This feature is referred to as Hidden Refresh.

The 64K RAM from Mostek is the culmination of several years of circuit and process development, proven in predecessor products.

#### PIN OUT

DUAL-IN-LINE PACKAGE

#### LEADLESS CHIP CARRIER

Address Inputs

Column Address

Strobe

Data In

Data Out

## **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on V <sub>CC</sub> supply relative to V <sub>SS</sub> | 1.0 V to +7.0 V |

|---------------------------------------------------------------|-----------------|

| Operating Temperature, T <sub>A</sub> (Ambient)               | 0°C to +70C     |

| Storage Temperature (Ceramic)                                 | 65°C to +150°C  |

| Storage Temperature (Plastic)                                 | 55°C to +125°C  |

| Power Dissipation                                             | 1 Watt          |

| Short Circuit Output Current                                  | 50 mA           |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **RECOMMENDED DC OPERATING CONDITIONS**

$(0^{\circ}C \le T_{A} \le 70^{\circ}C)$

| SYM             | PARAMETER                                   | MIN  | ТҮР | MAX                | UNITS | NOTES |

|-----------------|---------------------------------------------|------|-----|--------------------|-------|-------|

| V <sub>cc</sub> | Supply Voltage                              | 4.5  | 5.0 | 5.5                | V     | 1     |

| V <sub>IH</sub> | Input High (Logic 1) Voltage,<br>All Inputs | 2.4  | _   | V <sub>CC</sub> +1 | V     | 1     |

| VIL             | Input Low (Logic 0)<br>Voltage, All Inputs  | -2.0 | -   | .8                 | V     | 1,18  |

# DC ELECTRICAL CHARACTERISTICS

$(0^{\circ}C \le T_A \le 70^{\circ}C) (V_{CC} = 5.0 V \pm 10\%)$

| SYM                                | PARAMETER                                                                                                                                                                                        | MIN | MAX  | UNITS  | NOTES |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|--------|-------|

| I <sub>CC1</sub>                   | OPERATING CURRENT<br>Average power supply operating current<br>(RAS, CAS cycling; t <sub>RC</sub> = 330 ns)                                                                                      |     | 54.0 | mA     | 2     |

| I <sub>CC2</sub>                   | STANDBY CURRENT<br>Power supply standby current ( $\overline{RAS} = V_{H}$ ,<br>D <sub>OUT</sub> = High Impedance)                                                                               |     | 4    | mA     |       |

| I <sub>CC3</sub>                   | $\label{eq:RAS} \begin{array}{l} \hline RAS & ONLY REFRESH CURRENT \\ Average power supply current, refresh mode \\ \hline (RAS cycling, \hline CAS = V_{IH}; t_{RC} = t_{RC} min.) \end{array}$ |     | 45   | mA     | 2     |

| I <sub>CC4</sub>                   | PAGE MODE CURRENT<br>Average power supply current, page mode<br>operation (RAS = $V_{IL}$ , $t_{RAS} = t_{RAS}$ max., CAS<br>cycling; $t_{PC} = t_{PC}$ min.)                                    |     | 40   | mA     | 2     |

| I <sub>I(L)</sub>                  | INPUT LEAKAGE<br>Input leakage current, any input<br>(0 V $\leq$ V <sub>IN</sub> $\leq$ V <sub>CC</sub> ), all other pins not under<br>test = 0 V                                                | -10 | 10   | μΑ     |       |

| I <sub>O(L)</sub>                  | OUTPUT LEAKAGE<br>Output leakage current (D <sub>OUT</sub> is disabled,<br>0 V $\leq$ V <sub>OUT</sub> $\leq$ V <sub>CC</sub> )                                                                  | -10 | 10   | μΑ     |       |

| V <sub>OH</sub><br>V <sub>OL</sub> | OUTPUT LEVELS<br>Output High (Logic 1) voltage (I <sub>OUT</sub> = -5 mA)<br>Output Low (Logic 0) voltage (I <sub>OUT</sub> = 4.2 mA)                                                            | 2.4 | 0.4  | V<br>V |       |

#### NOTES:

- 1. All voltages referenced to VSS.

- 2.  $I_{CC}$  is dependent on output loading and cycle rates. Specified values are obtained with the output open.

- 3. An initial pause of 500  $\mu s$  is required after power-up followed by any 8  $\overline{RAS}$  cycles before proper device operation is achieved. Note that  $\overline{RAS}$  may be cycled during the initial pause.

- 4. AC characteristics assume t<sub>T</sub> = 5 ns.

- 5. V<sub>IH</sub> min. and V<sub>IL</sub> max. are reference levels for measuring timing of input signals. Transition times are measured between V<sub>IH</sub> and V<sub>IL</sub>.

- 6. The minimum specifications are used only to indicate cycle time at which proper operation over the full temperature range (0°C  $\leq$  T\_A  $\leq$  70°C) is assured.

- 7. Load = 2 TTL loads and 50 pF.

- 8. Assumes that  $t_{RCD} \leq t_{RCD}$  (max). If  $t_{RCD}$  is greater than the maximum recommended value shown in this table,  $t_{RAC}$  will increase by the amount that  $t_{RCD}$  exceeds the value shown.

- 9. Assumes that  $t_{RCD} \ge t_{RCD}$  (max).

- 10. t<sub>OFF</sub> max defines the time at which the output achieves the open circuit condition and is not referenced to  $V_{OH}$  or  $V_{OL}$ .

- 11. Operation within the  $t_{RCD}$  (max) limit insures that  $t_{RAC}$  (max) can be met.  $t_{RCD}$  (max) is specified as a reference point only; if  $t_{RCD}$  is greater than the

specified  $t_{RCD}$  (max) limit, then access time is controlled exclusively by  $\underline{t}_{CAC}$

- 12. Either tRRH or tRCH must be satisfied for a read cycle.

- 13. These parameters are referenced to CAS leading edge in early write cycles and to WRITE leading edge in delayed write or read-modify-write cycles.

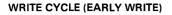

- 14. twcs, t<sub>CWD</sub>, and t<sub>RWD</sub> are restrictive operating parameters in READ/WRITE and READ/MODIFY/WRITE cycles only. If t<sub>WCS</sub>  $\geq$  twccs (min) the cycle is an EARLY WRITE cycle and the data output will remain open circuit throughout the entire cycle. If t<sub>CWD</sub>  $\geq$  t<sub>CWD</sub> (min) and t<sub>RWD</sub>  $\geq$  t<sub>RWD</sub> (min) the cycle is a READ/WRITE and the data output will contain data read from the selected cell. If neither of the above conditions are met the condition of the data out (at access time and until CAS goes back to V<sub>IH</sub>) is indeterminate.

- 15. In addition to meeting the transition rate specification, all input signals must transmit between  $V_{I\!H}$  and  $V_{I\!L}$  (or between  $V_{I\!L}$  and  $V_{I\!H}$ ) in a monotonic manner.

- 16. Effective capacitance calculated from the equation  $C = I \Delta t$  with  $\Delta V = 3$  volts and power supply at nominal level.  $\Delta V$

- 17. CAS = VIH to disable DOUT

- 18. Includes the DC level and all instantaneous signal excursions.

- 19. WRITE = don't care. Data out depends on the state of CAS. If CAS = V<sub>IH</sub>, data output is high impedance. If CAS = V<sub>IL</sub>, the data output will contain data from the last valid read cycle.

# ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS (3,4,5,15) (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C), V<sub>CC</sub> = 5.0 V $\pm$ 10%

| SYM                          | BOL              |                                            | MK4 | 564-15 | MK4564-20 |        |       |       |

|------------------------------|------------------|--------------------------------------------|-----|--------|-----------|--------|-------|-------|

| STD                          | ALT              | PARAMETER                                  | MIN | MAX    | MIN       | MAX    | UNITS | NOTES |

| t <sub>RELREL</sub>          | t <sub>RC</sub>  | Random read or write cycle time            | 260 |        | 330       |        | ns    | 6,7   |

| t <sub>RELREL</sub><br>(RMW) | t <sub>RMW</sub> | Read modify write cycle time               | 300 |        | 390       |        | ns    | 6,7   |

| t <sub>RELREL</sub><br>(PC)  | t <sub>PC</sub>  | Page mode cycle time                       | 155 |        | 200       |        | ns    | 6,7   |

| t <sub>RELQV</sub>           | t <sub>RAC</sub> | Access time from RAS                       |     | 150    |           | 200    | ns    | 7,8   |

| t <sub>CELQV</sub>           | t <sub>CAC</sub> | Access time from CAS                       |     | 85     |           | 115    | ns    | 7,9   |

| t <sub>CEHOZ</sub>           | t <sub>OFF</sub> | Output buffer turn-off delay               | 0   | 40     | 0         | 50     | ns    | 10    |

| t <sub>T</sub>               | t <sub>T</sub>   | Transition time (rise and fall)            | 3   | 50     | 3         | 50     | ns    | 5,15  |

| t <sub>REHREL</sub>          | t <sub>RP</sub>  | RAS precharge time                         | 100 |        | 120       |        | ns    |       |

| t <sub>RELREH</sub>          | t <sub>RAS</sub> | RAS pulse width                            | 150 | 10,000 | 200       | 10,000 | ns    |       |

| t <sub>CELREH</sub>          | t <sub>RSH</sub> | RAS hold time                              | 85  |        | 115       |        | ns    |       |

| t <sub>RELCEH</sub>          | <sup>t</sup> сsн | CAS hold time                              | 150 |        | 200       |        | ns    |       |

| t <sub>CELCEH</sub>          | t <sub>CAS</sub> | CAS pulse width                            | 85  | 10,000 | 115       | 10,000 | ns    |       |

| t <sub>RELCEL</sub>          | t <sub>RCD</sub> | RAS to CAS delay time                      | 20  | 65     | 25        | 85     | ns    | 11    |

| t <sub>REHWX</sub>           | t <sub>RRH</sub> | Read command hold time referenced to RAS   | 20  |        | 25        |        | ns    | 12    |

| t <sub>AVREL</sub>           | t <sub>ASR</sub> | Row address set-up time                    | 0   |        | 0         |        | ns    |       |

| t <sub>RELAX</sub>           | t <sub>RAH</sub> | Row address hold time                      | 20  |        | 25        |        | ns    |       |

| t <sub>AVCEL</sub>           | t <sub>ASC</sub> | Column address set-up time                 | 0   |        | 0         |        | ns    |       |

| t <sub>CELAX</sub>           | t <sub>CAH</sub> | Column address hold time                   | 25  |        | 35        |        | ns    |       |

| t <sub>RELA(C)</sub> X       | t <sub>AR</sub>  | Column address hold time referenced to RAS | 90  |        | 120       |        | ns    |       |

# ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS (Continued)

,

(3,4,5,15) (0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C), V<sub>CC</sub> = 5.0V  $\pm$  10%

| SYMBOL                      |                  |                                                  | MK4564-15 |     | MK4564-20 |     |       | Τ     |

|-----------------------------|------------------|--------------------------------------------------|-----------|-----|-----------|-----|-------|-------|

| STD                         | ALT              | PARAMETER                                        | MIN       | MAX | MIN       | MAX | UNITS | NOTES |

|                             | t <sub>RCS</sub> | Read command set-up time                         | 0         |     | 0         |     | ns    |       |

| t <sub>CEHWX</sub>          | t <sub>RCH</sub> | Read command hold time referenced to CAS         | 0         |     | 0         |     | ns    | 12    |

| t <sub>CELWX</sub>          | <sup>t</sup> wcн | Write command hold time                          | 35        |     | 55        |     | ns    |       |

| t <sub>RELWX</sub>          | twcr             | Write command hold time referenced to RAS        | 100       |     | 140       |     | ns    |       |

| t <sub>WLWH</sub>           | t <sub>WP</sub>  | Write command pulse width                        | 25        |     | 45        |     | ns    |       |

| t <sub>WLREH</sub>          | t <sub>RWL</sub> | Write command to RAS lead time                   | 35        |     | 55        |     | ns    |       |

| t <sub>WLCEH</sub>          | t <sub>CWL</sub> | Write command to CAS lead time                   | 35        |     | 55        |     | ns    |       |

| t <sub>DVCEL</sub>          | t <sub>DS</sub>  | Data-in set-up time                              | 0         |     | 0         |     | ns    | 13    |

| t <sub>CELDX</sub>          | t <sub>DH</sub>  | Data-in hold time                                | 30        |     | 55        |     | ns    | 13    |

| t <sub>reldx</sub>          | t <sub>DHR</sub> | Data-in hold time<br>referenced to RAS           | 95        |     | 140       |     | ns    |       |

| t <sub>CEHCEL</sub><br>(PC) | t <sub>CP</sub>  | CAS precharge time<br>(for page-mode cycle only) | 60        |     | 75        |     | ns    |       |

| t <sub>RVRV</sub>           | t <sub>REF</sub> | Refresh Period                                   |           | 2   |           | 2   |       | ms    |

| t <sub>WLCEL</sub>          | t <sub>wcs</sub> | WRITE command set-up time                        | 10        |     | -10       |     | ns    | 14    |

| t <sub>CELWL</sub>          | t <sub>CWD</sub> | CAS to WRITE delay                               | 55        |     | 80        |     | ns    | 14    |

| t <sub>RELWL</sub>          | t <sub>RWD</sub> | RAS to WRITE delay                               | 120       |     | 165       |     | ns    | 14    |

| t <sub>CEHCEL</sub>         | t <sub>CPN</sub> | CAS precharge time                               | 30        |     | 35        |     | ns    |       |

# AC ELECTRICAL CHARACTERISTICS

$(0^{\circ} \le T_{A} \le 70^{\circ}C)$ ,  $V_{CC} = 5.0 V \pm 10\%$

| SYM             | PARAMETER                                                             | МАХ | UNITS | NOTES |

|-----------------|-----------------------------------------------------------------------|-----|-------|-------|

| C <sub>I1</sub> | Input Capacitance (A <sub>0</sub> - A <sub>7</sub> ), D <sub>IN</sub> | 5   | pF    | 16    |

| C <sub>I2</sub> | Input Capacitance RAS, CAS, WRITE                                     | 10  | pF    | 16    |

| C <sub>0</sub>  | Output Capacitance (D <sub>OUT</sub> )                                | 7   | pF    | 16,17 |

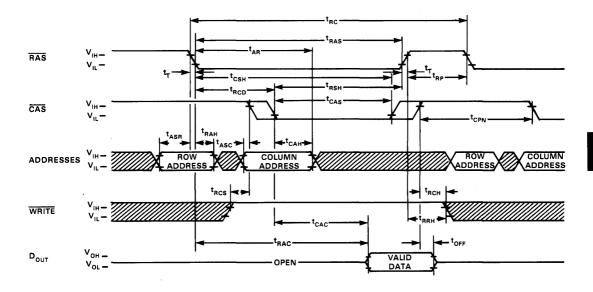

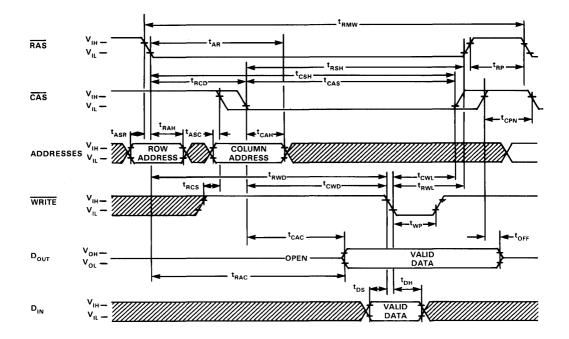

# READ CYCLE

IV

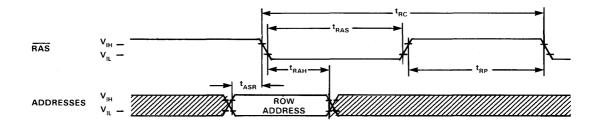

# **"RAS-ONLY" REFRESH CYCLE**

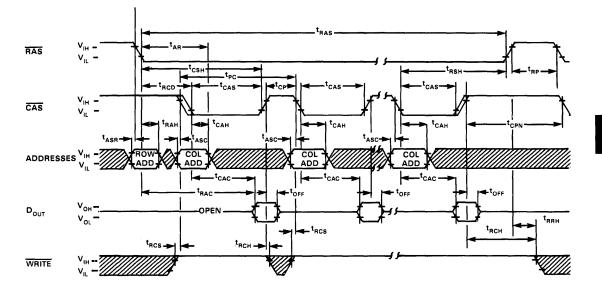

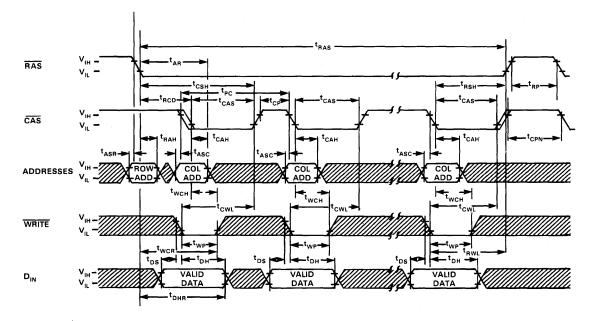

# PAGE MODE WRITE CYCLE

### OPERATION

The eight address bits required to decode 1 of the 65,536 cell locations within the MK4564 are multiplexed onto the eight address inputs and latched into the on-chip address latches by externally applying two negative going TTL-level clocks. The first clock, Row Address Strobe (RAS), latches the eight row addresses into the chip. The high-to-low transition of the second clock, Column Address Strobe (CAS), subsequently latches the eight column addresses into the chip. Each of these signals, RAS and CAS, triggers a sequence of events which are controlled by different delayed internal clocks. The two clock chains are linked together logically in such a way that the address multiplexing operation is done outside of the critical timing path for read data access. The later events in the CAS clock sequence are inhibited until the occurrence of a delayed signal derived from the RAS clock chain. This "gated CAS" feature allows the CAS clock to be externally activated as soon as the Row Address Hold specification (t<sub>RAH</sub>) has been satisfied and the address inputs have been changed from Row address to Column address information.

The "gated CAS" feature permits CAS to be activated at any time after  $t_{RAH}$  and it will have no effect on the worst case data access time  $(t_{RAC})$  up to the point in time when the delayed row clock no longer inhibits the remaining sequence of column clocks. Two timing endpoints result from the internal gating of CAS which are called  $t_{RCD}$  (min) and  $t_{RCD}$  (max). No data storage or reading errors will result if CAS is applied to the MK4564 at a point in time beyond the  $t_{RCD}$  (max) limit. However, access time will then be determined exclusively by the access time from CAS ( $t_{CAC}$ ) rather than from RAS ( $t_{RAC}$ ), and RAS access the  $t_{RCD}$  (max) limit.

#### DATA INPUT/OUTPUT

Data to be written into a selected <u>cell</u> is latched into an on-chip register by a combination of WRITE and CAS while RAS is active. The latter of WRITE or CAS to make its negative transition is the strobe for the Data In (D<sub>IN</sub>) register. This permits several options in the write cycle timing. In a write cycle, if the WRITE input is brought low (active) prior to CAS being brought low (active), the D<sub>IN</sub> is strobed by CAS, and the Input Data set-up and hold times are referenced to CAS. If the input data is not available at CAS time (late write) or if it is desired that the cycle be a read-write or readmodify-write cycle the WRITE signal should be delayed until after CAS has made its negative transition. In this "delayed write cycle" the data input set-up and hold times are referenced to the negative edge of WRITE rather than CAS.

Data is retrieved from the memory in a read cycle by maintaining  $\overline{WRITE}$  in the inactive or high state throughout the portion of the memory cycle in which both the  $\overline{RAS}$  and  $\overline{CAS}$  are low (active). Data read from the selected cell is available at the output port within the specified access time. The output data is the same polarity (not inverted) as the input data.

#### DATA OUTPUT CONTROL

The normal condition of the Data Output ( $D_{OUT}$ ) of the MK4564 is the high impedance (open-circuit) state; anytime CAS is high (inactive) the  $D_{OUT}$  pin will be floating. Once the output data port has gone active, it will remain valid until CAS is taken to the precharge (inactive high) state.

#### PAGE MODE OPERATION

The Page Mode feature of the MK4564 allows for successive memory operations at multiple column locations within the same row address. This is done by strobing the row address into the chip and maintaining the RAS signal low (active) throughout all successive memory cycles in which the row address is common. The first access within a page mode operation will be available at  $t_{RAC}$  or  $t_{CAC}$  time, whichever is the limiting parameter. However, all successive accesses within the page mode operation will be available at  $t_{CAC}$  time (referenced to  $\overline{CAS}$ ). With the MK4564 this results in approximately a 45% improvement in access times. Effective memory cycle times are also reduced when using page mode.

The page mode boundary of a single MK4564 is limited to the 256 column locations determined by all combinations of the eight column address bits. Operations within the page boundary need not be sequentially addressed and any combination of read, write, and read-modify-write cycles is permitted within the page mode operation.

#### REFRESH

Refresh of the dynamic cell matrix is accomplished by performing a memory cycle at each of the 128 row addresses within each 2ms interval. Although any normal memory cycle will perform the required refreshing, this function is most easily accomplished with "RAS-only" cycles.

The RAS-only refresh cycle requires that a 7 bit refresh address (AO-A6) be valid at the device address inputs when RAS goes low (active). The state of the output data port during a RAS-only refresh is controlled by CAS. If CAS is high (inactive) during the entire time that RAS is asserted, the output will remain in the high impedance state. If CAS is low (active) the entire time that RAS is asserted, the output will remain in the same state that it was prior to the issuance of the RAS signal. If CAS makes a low-to-high transition during the RAS-only refresh cycle, the output data buffer will assume the high impedance state. However, CAS may not make a high to low transition during the RAS-only refresh cycle interprets this as a normal RAS/CAS (read or write) type cycle.

# **HIDDEN REFRESH**

A  $\overline{RAS}$ -only refresh cycle may take place while maintaining valid output data by extending the  $\overline{CAS}$  active time from a previous memory read cycle. This feature is referred to as a hidden refresh. (See figure below.)

# HIDDEN REFRESH CYCLE (SEE NOTE 19)

IV